티스토리 뷰

프로그램 스케줄을 보니 굉장히 많은 세션들이 준비돼 있었다. Plenary talk이 끝나고 제일 관심 있는 Packaging and Heterogeneous Integration에 해당되는 룸으로 찾아갔다.

AI 반도체와 패키징

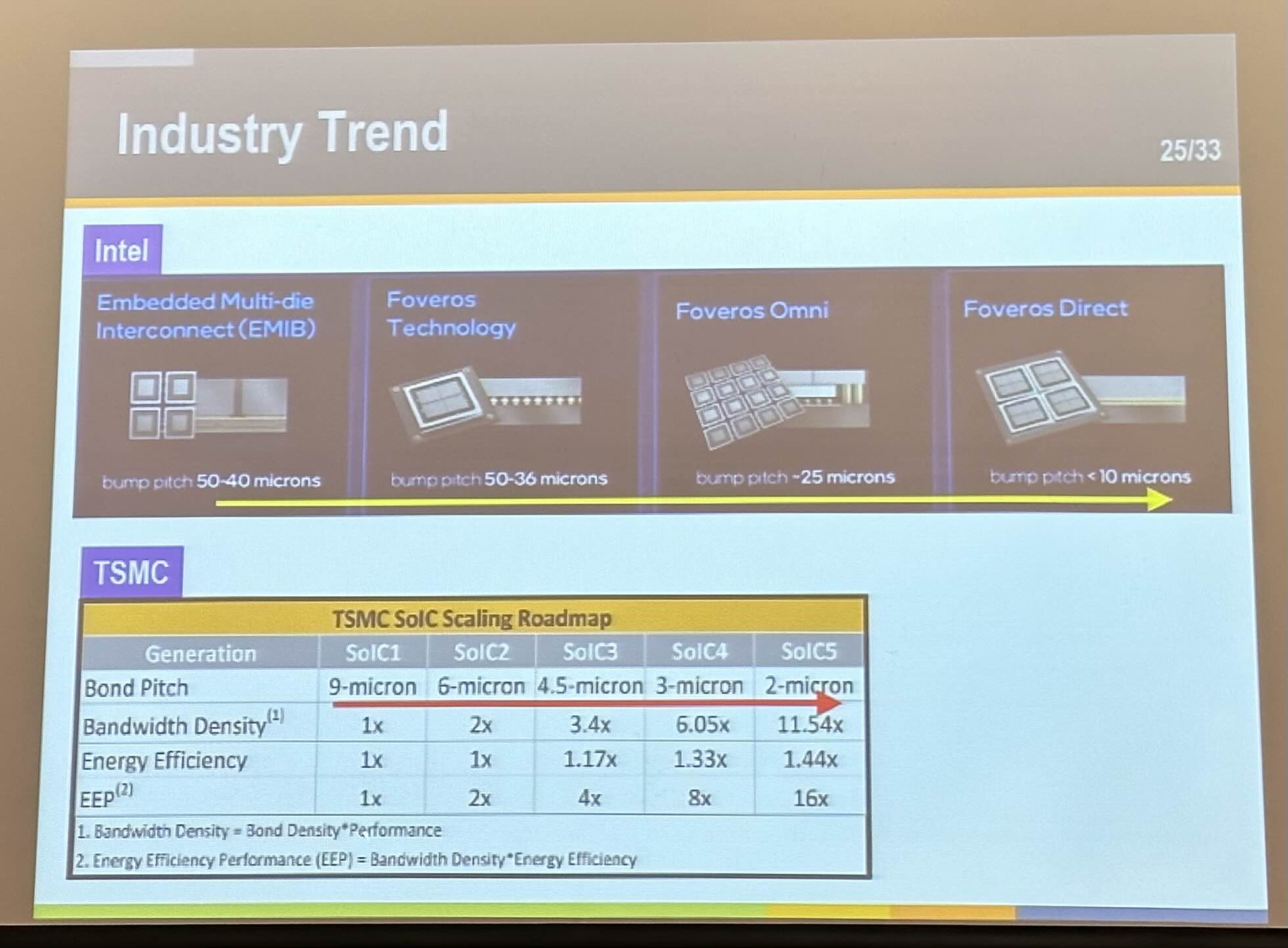

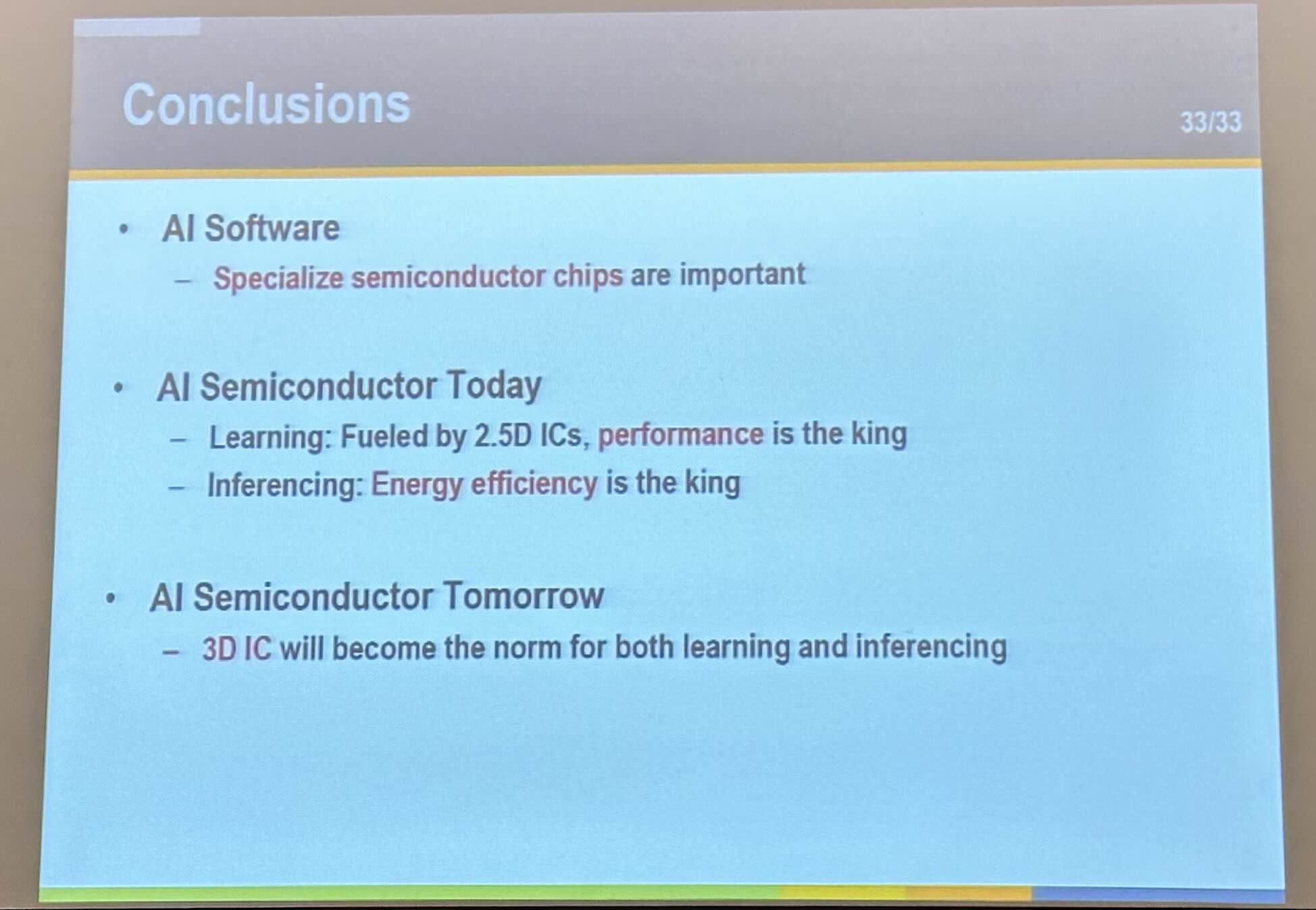

제일 처음에는 AI Semiconductor Chips Using Heterogeneous Integration: Why the Hype and What Next?라는 주제의 키노트로 시작했다. 발표자는 조지아텍의 한국인 교수님이었는데 발표를 자신 있고, 스스로 재미있게 하셨다. 엄청 프로페셔널한 느낌이었다. 키노트의 핵심은 결국 AI를 수행하기 위해 특화된 칩을 만들고 여러 개로 쪼개지며 쌓는 기술이 발전한다는 것.

새로운 패키징 기술

1. IMS (Injection Molded Solder)

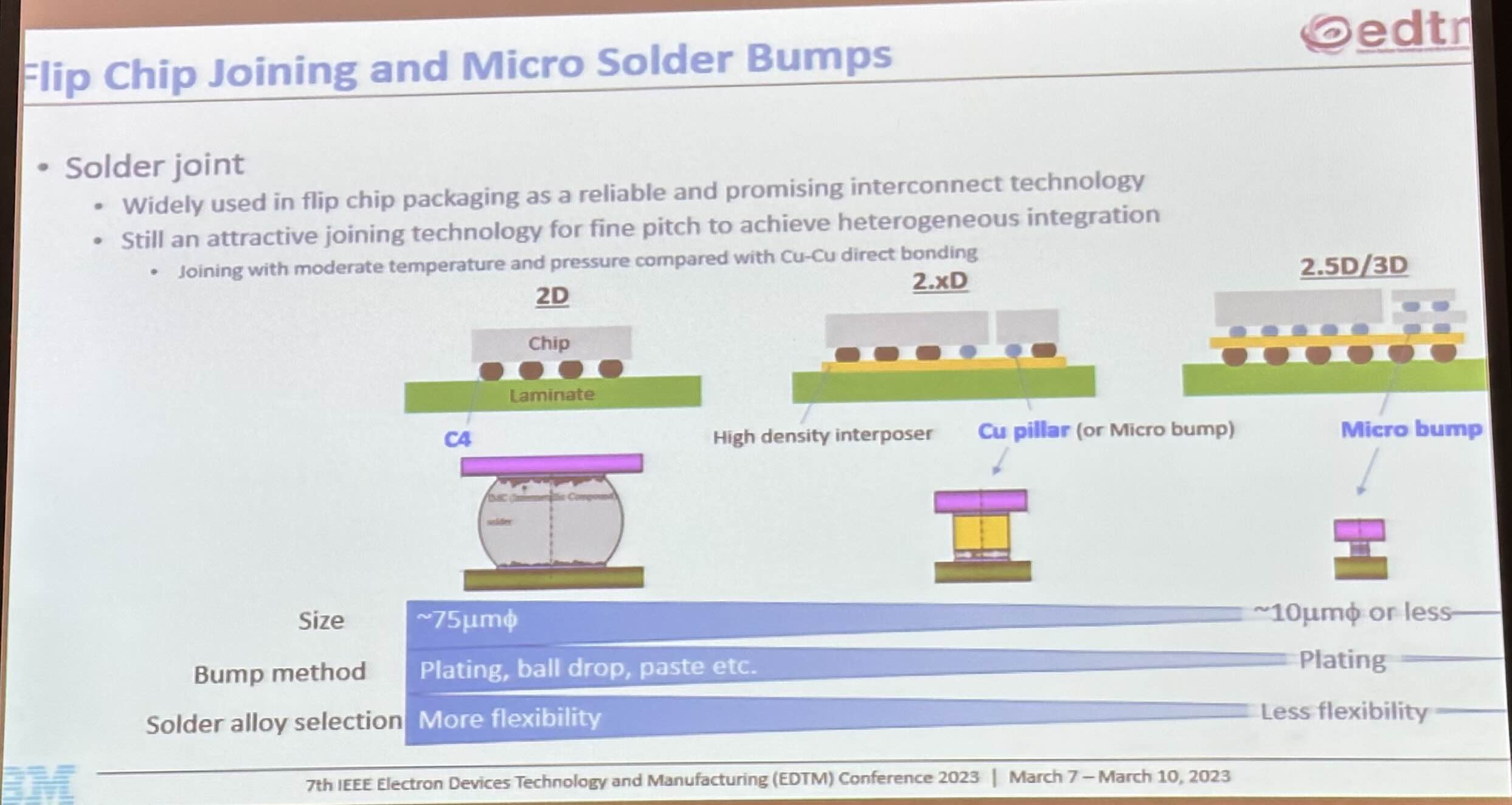

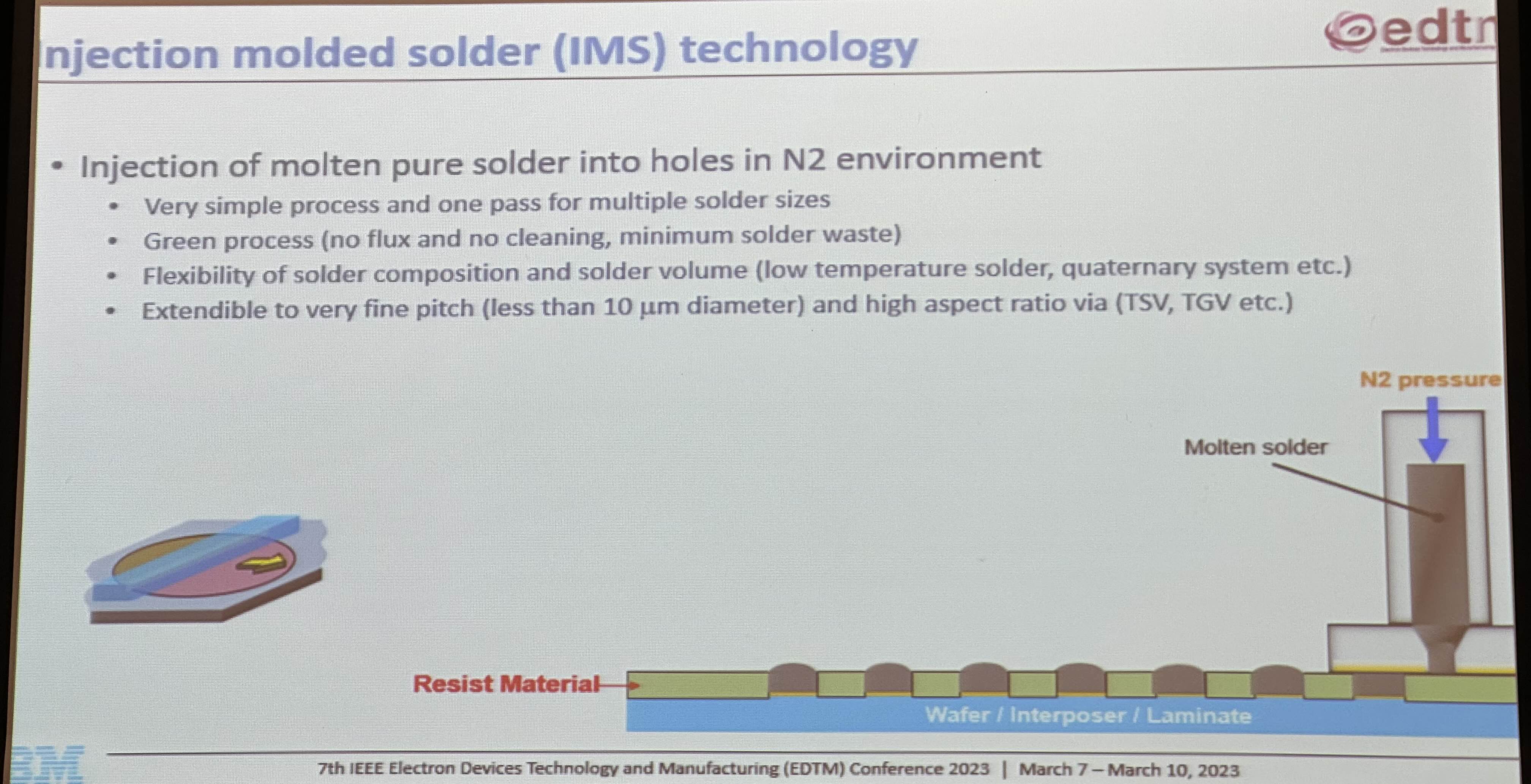

다음으로 새로운 본딩 기술인 IBM의 Injection Molded Solder (IMS)가 소개됐다. 패키징을 위한 주요 공정인 기존 Flip chip 본딩 타입에서는 칩과 기판을 연결시키기 위해 Wafer에 Plating 방식으로 Solder Bump를 형성한다.

(Flip chip 본딩에 대한 설명은 아래 링크 클릭!)

https://simguani.tistory.com/4

반도체 후공정, 패키징

지난번엔 OSAT 회사에 대해 알아봤는데, 이번에는 반도체 후공정 OSAT 회사들이 담당하는 패키징 공정에 대해 알아보자. 뉴스를 보면 TSMC나 삼성전자 등 파운드리 회사에서 5 나노, 3 나노 공정

simguani.tistory.com

그러나 IMS는 Plating 방식이 아닌 Molten solder를 주사하여 형성한다는 것이다. 기존 Plating 방식보다 간단하고 친환경적이라는 장점이 있다고 한다.

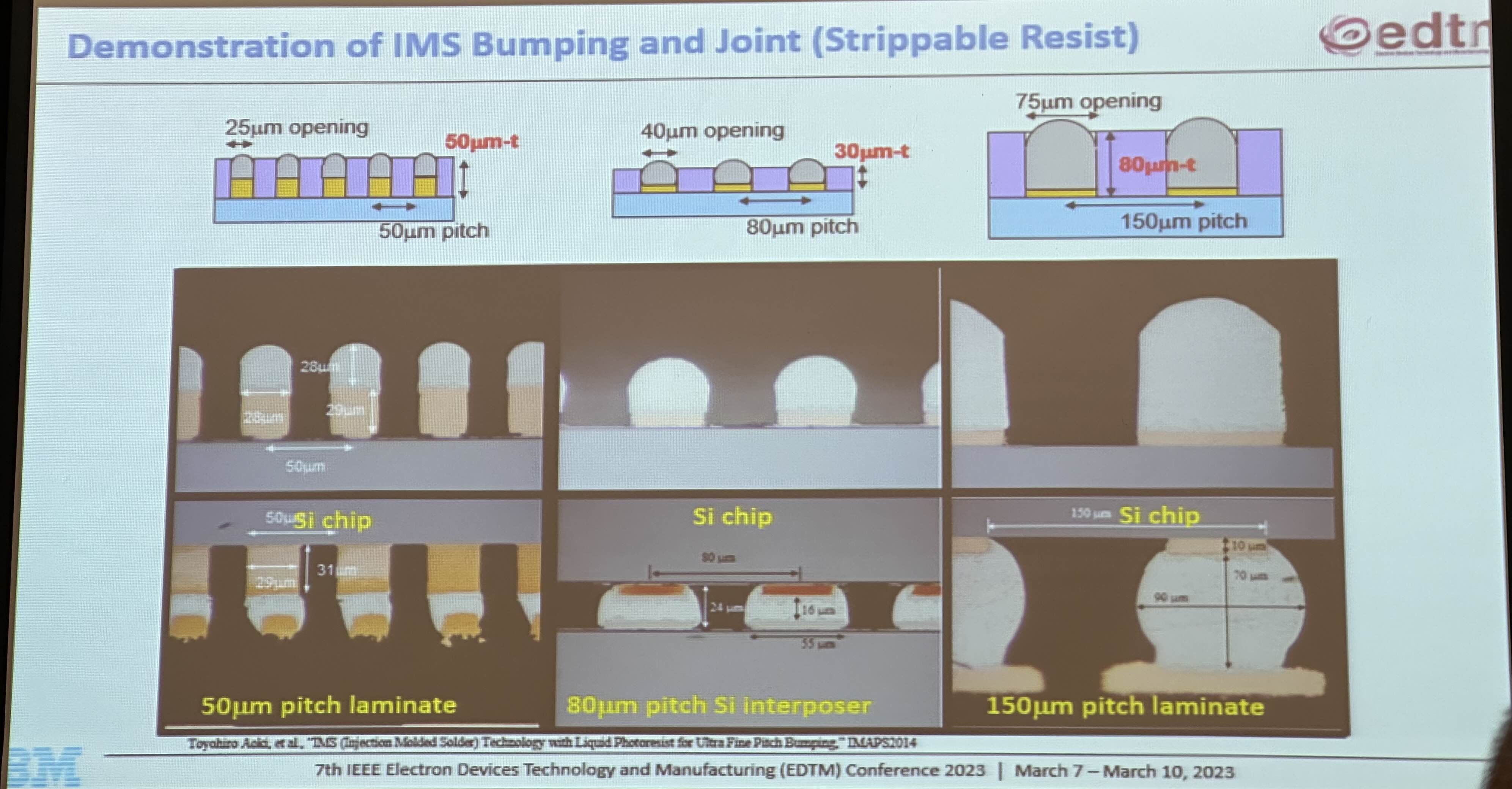

아래는 Advanced PKG로 변해감에 따라 범프 Pitch가 미세화되고 있어 계속 작아지는 범프 형성에 한계가 있다는 것이다.

IMS는 이러한 Fine pitch에 대응할 수 있는 기술이라고 한다. 양산 가능한 수준의 신뢰성 데이터를 확보했다고 한다.

2. Hybrid bonding

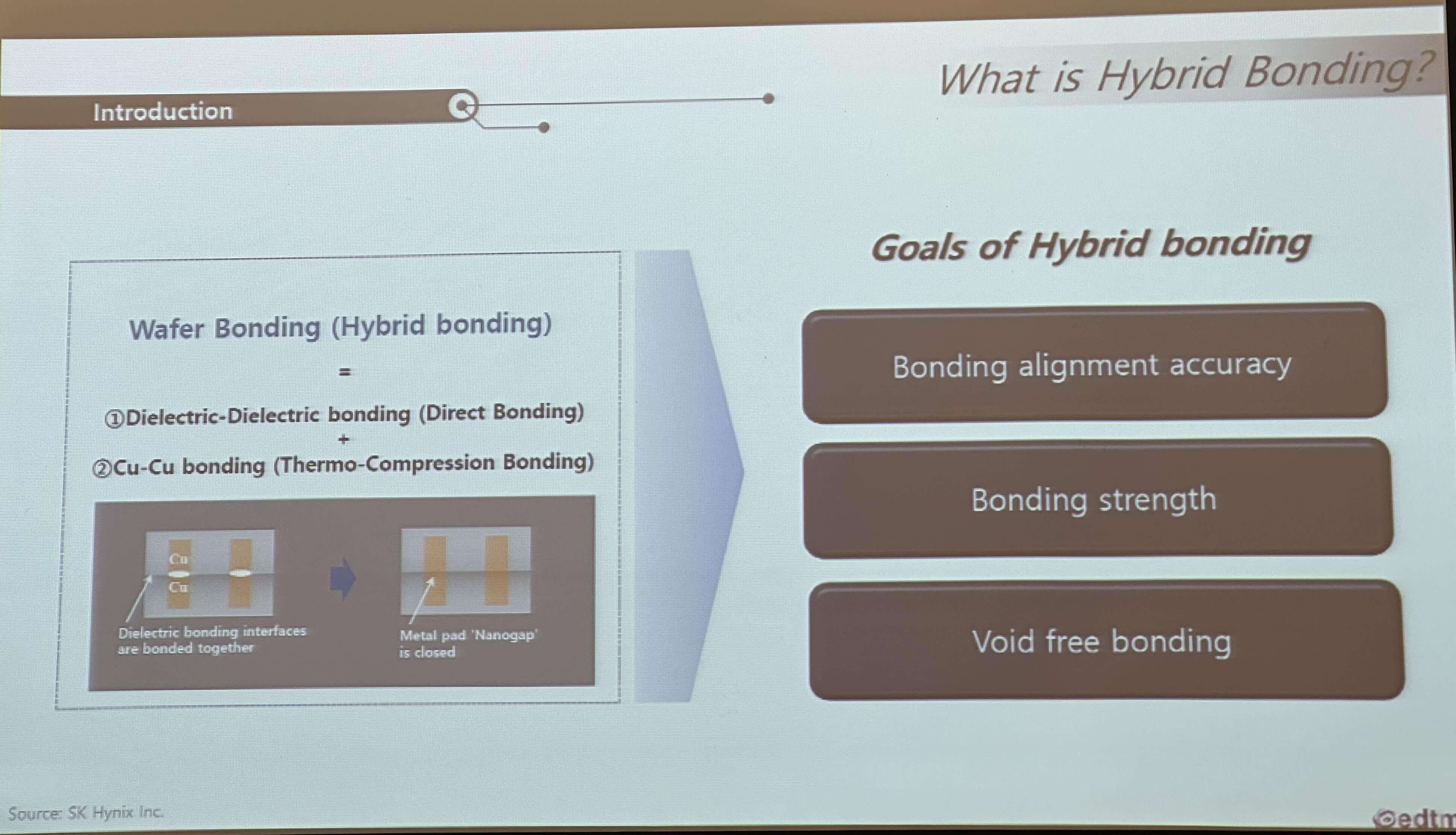

또 다른 기술로 SK하이닉스에서 최근 떠오르는 Hybrid bonding에 대해 발표했다. 이 본딩 기술은 칩과 기판을 붙이는 것이 아니라 Chip to chip 본딩 기술이다. HPC, 서버 등 고사양 반도체는 칩과 칩을 연결시키는 기술이 필요하다. 칩이 여러 개로 쪼개져 위로 쌓는 2.5D, 3D 등 Advanced 패키징 구조로 변해가고 있기 때문이다.

(Advanced 패키징에 대한 자세한 내용은 아래 링크로!)

https://simguani.tistory.com/9

Fab 공정의 한계와 Advanced 패키징

Fab 공정의 한계 요즘 기사를 보면 파운드리 업체들의 Fab node 기술인 나노 경쟁이 치열하다. 최근 삼성전자가 세계 최초로 3 나노 공정 양산을 시작했다고 한다. 그러나 TSMC의 3 나노와 같은 성능

simguani.tistory.com

Hybrid bonding은 두 가지 소재의 본딩을 한 번에 이뤄지게 한다는 의미이다. Cu to Cu와 Si to Si 본딩을 한 번에 진행한다. 두개의 wafer를 맞대어 붙이는 것인데, 각 Wafer에 형성돤 Cu pad의 Align을 맞추어 붙인 후 열을 가해 Cu to Cu, Si to Si 본딩을 동시에 진행한다. Wafer level 본딩이기 때문에 기술적인 난이도가 높다.

Advanced 패키징 & Substrate

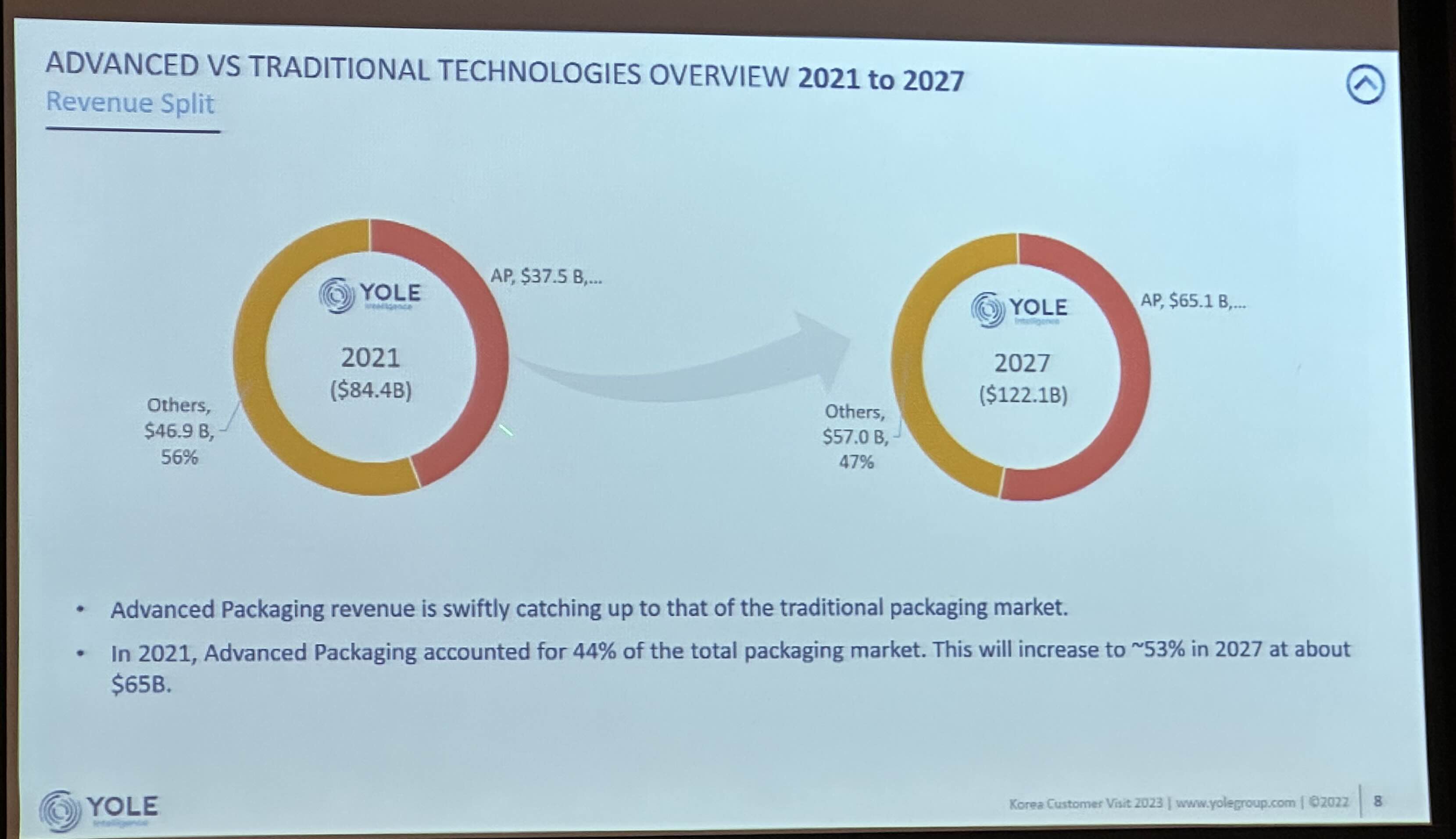

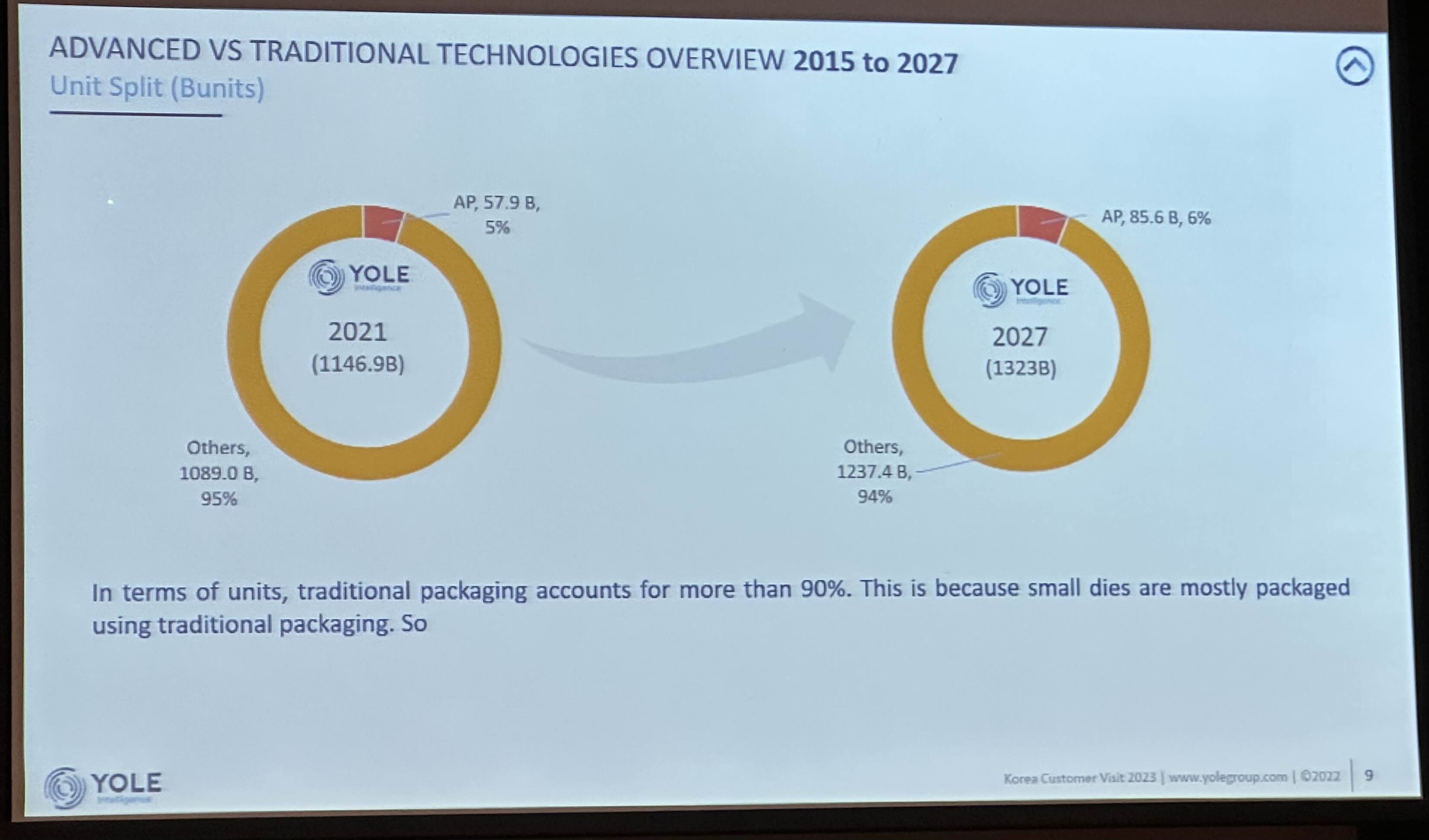

시장 조사 업체 Yole의 차세대 패키징, 기판 시장에 대해 발표했다. Advanced 패키징의 핵심은 Multi die이다. 칩이 많아졌는데 이것을 어떻게 효율적으로 붙일 것인가가 관건이다.

시장 규모를 보면 금액 측면에서 Advanced 패키징 시장의 비중이 더 커질 것으로 전망하고 있다. 다만 수량은 큰 변화가 없을 것이라고 전망하는데, 이건 기존의 저사양 Legacy 패키지가 작은 칩을 하나씩 붙였기 때문이다. 예를 들면 Advanced 패키지에는 칩이 5개부터 10개 이상씩 붙게 되는데 (HBM 포함) 이건 패키지 1개로 본다. 즉, 칩이 1개 붙는 저사양 패키지에 비해 패키지 수량은 적겠지만 1개의 패키지가 5~10개 이상의 칩을 수용하는 것이다.

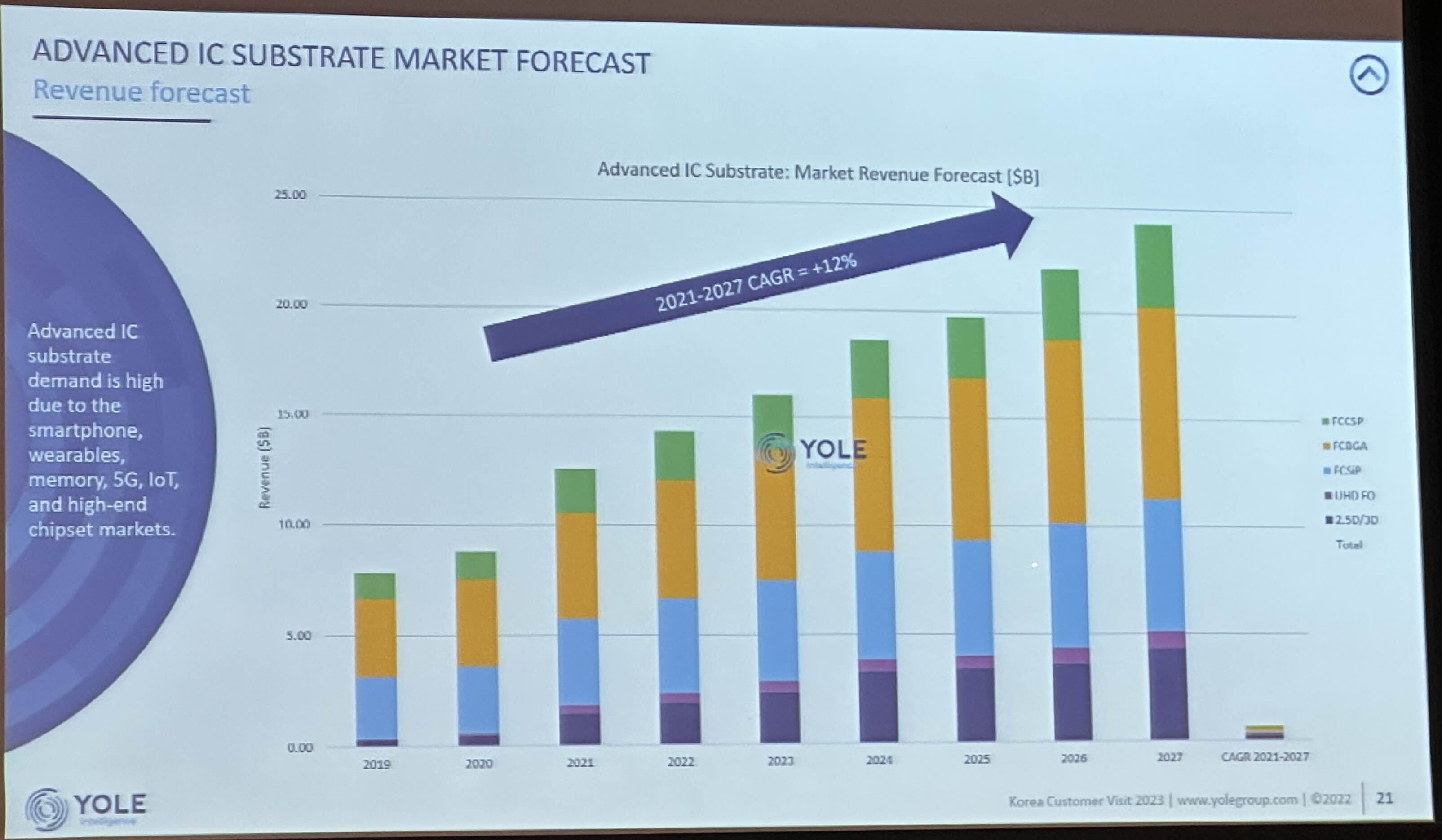

이에 따라서 Substrate (기판) 시장도 성장할 것으로 전망한다.

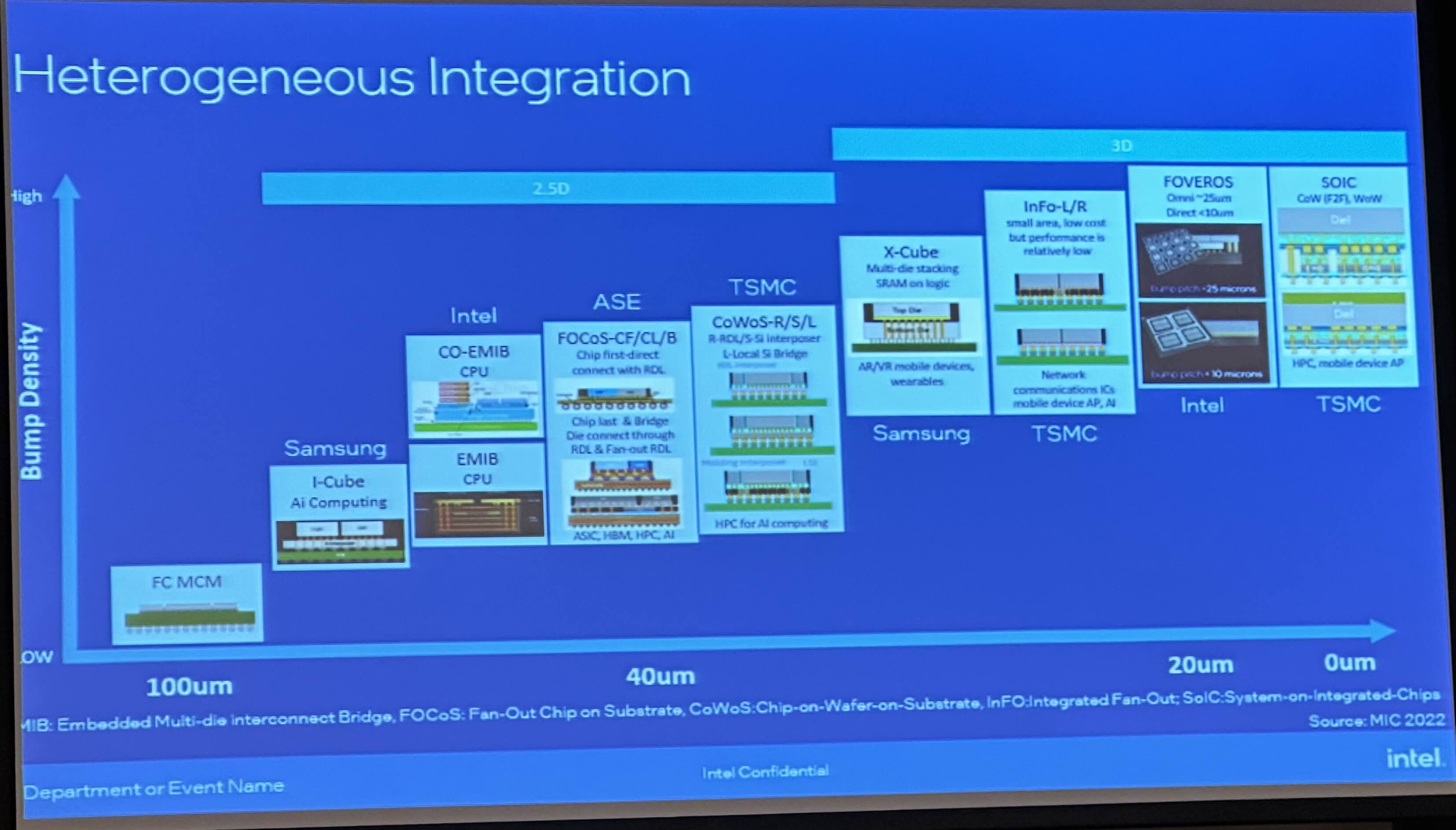

Substrate Trend

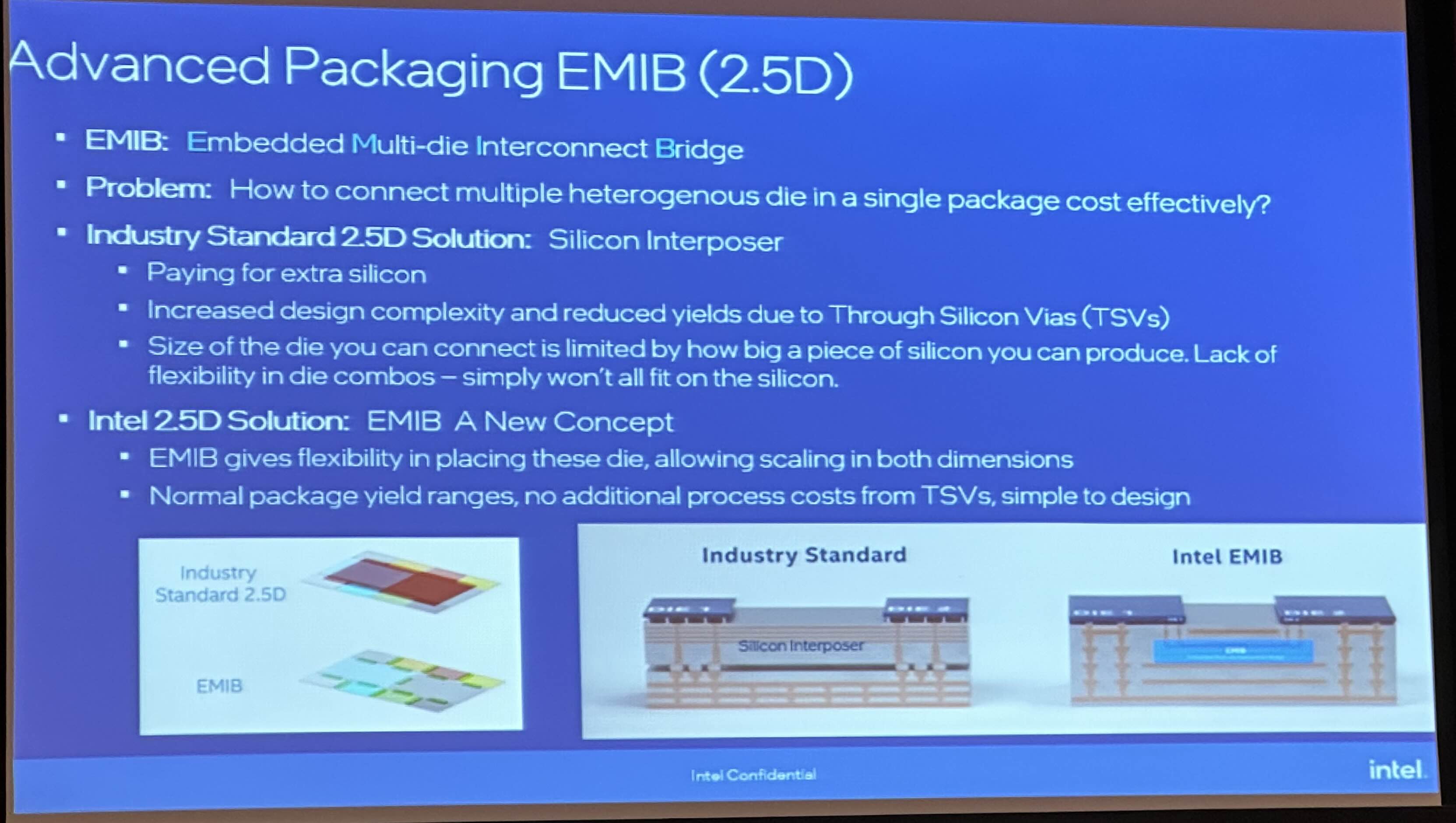

인텔에서는 Latest Interconnection Technologies and Package Substrate Trend라는 주제로 발표를 했다. 앞에서와 비슷한 이야기로, 여러 개로 쪼개지는 Chiplet으로 인해 이들을 연결시키기 위해 다양한 소재의 인터포저를 사용하여 2.5D, 3D 등 다양한 패키지 구조가 나오는 것이다.

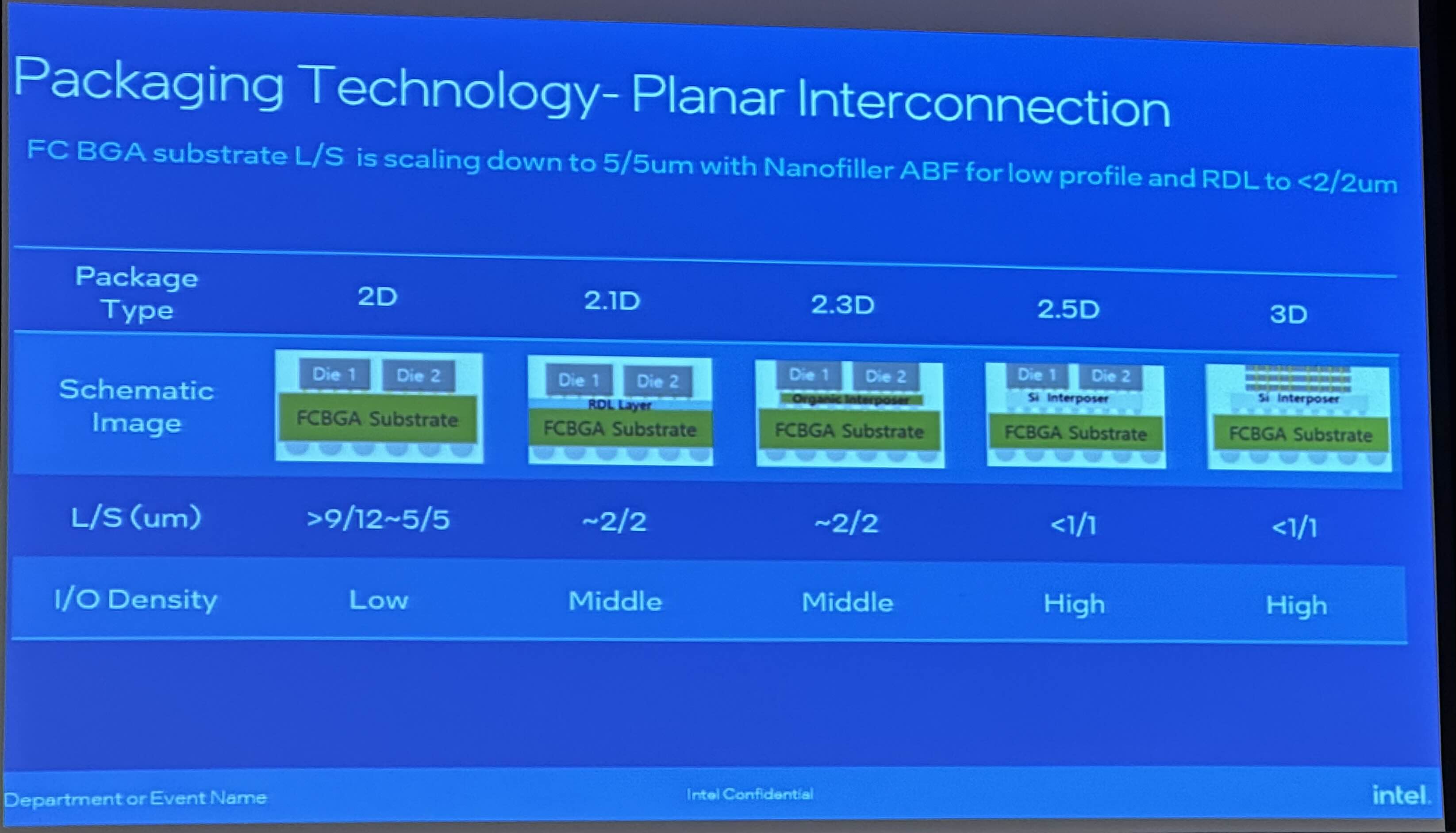

시장에 나와있는 업체별 2.5D, 3D 패키지와 2.xD 구조들을 정리해 주었다. 사실 2.1D, 2.3D. 2.5D 구조는 표준화되지 않아서 같은 구조라도 부르는 게 업체마다 다르다.

Si 인터포저가 적용된 것은 통상적으로 2.5D라고 부르는데, Si bridge가 적용된 EMIB는 2.5D라고 하기도, 2.1D라고 하기도 한다. 인텔에서는 2.5D라고 정의했다. EMIB는 인텔 특허니까 인텔이 부르는 대로 따라야겠다.

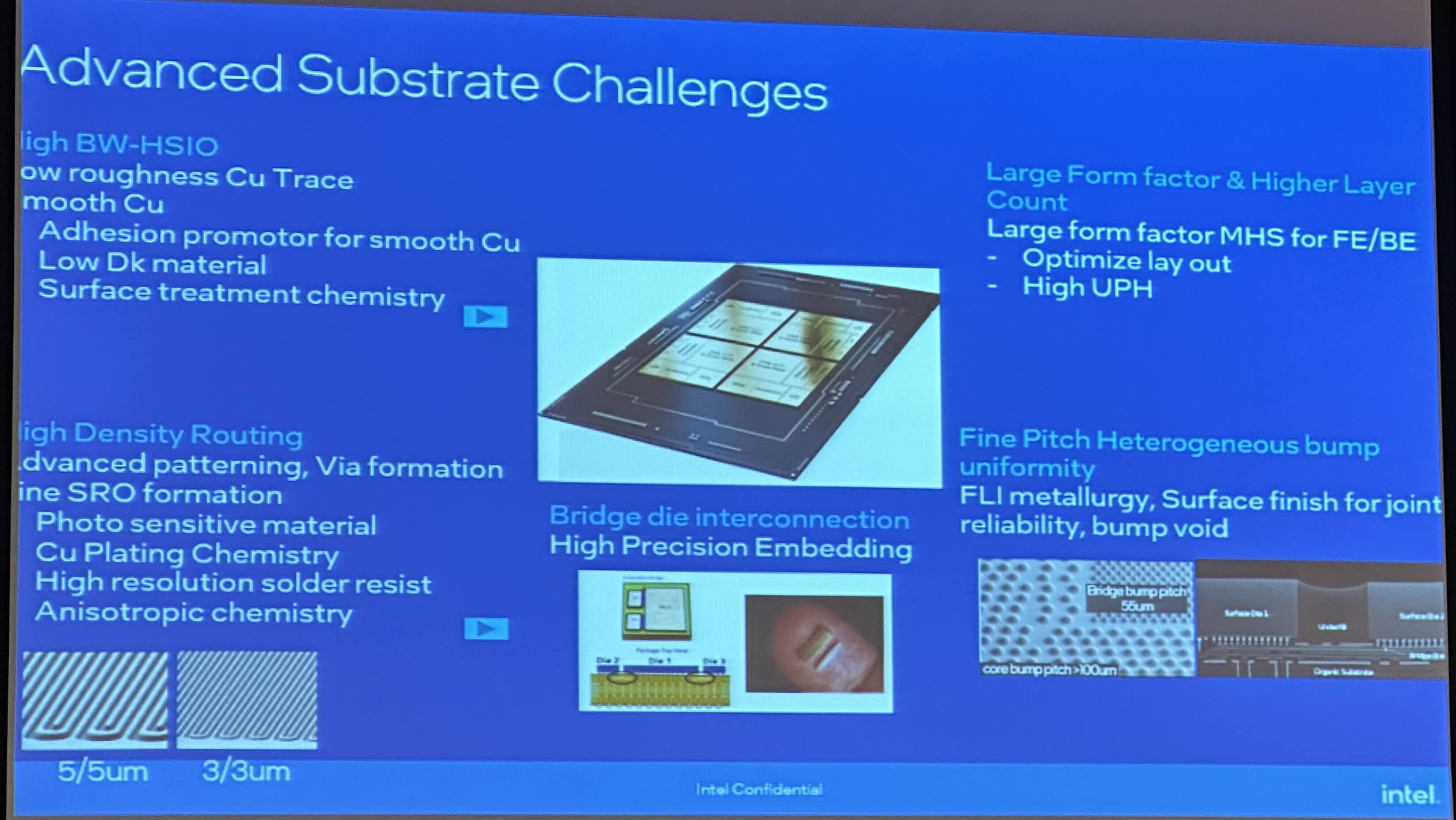

Advanced 패키징을 위해 기판을 만들 때도 점점 기술적인 어려움이 생기고 있다. 미세한 Line and space (회로 폭과 회로 간 간격), Size가 커짐에 따른 휨 문제, 칩을 실장 하는 패드의 Uniformity 등..

이외에도 카이스트 등 대학교에서 연구하고 있는 내용을 들을 수 있었다. 패키지가 커짐에 따라 Warpage (휘는 현상)를 개선하는 방법, 시뮬레이션 기술, 다양한 인터포저 기술 등에 대해 알 수 있었다. 내가 대학생 때만 해도 패키징에 대한 연구 논문이나 정보가 별로 없었던 것 같은데, 그만큼 중요해졌다는 게 느껴진다.

'전시 & 세미나 리뷰' 카테고리의 다른 글

| IEEE EDTM2023 컨퍼런스 반도체 학회 후기 (Feat. SK하이닉스) (0) | 2023.03.21 |

|---|---|

| CES2023 여정기 Day3 (2) | 2023.02.06 |

| CES2023 D-1 & Day-1 (3부) CES 전시 첫날 (0) | 2023.01.20 |

| CES2023 D-2 (2부) 힐튼 호텔 구경 & 부스 점검 (0) | 2023.01.15 |

| CES2023 D-3 (1부) 라스베가스 도착 (1) | 2023.01.12 |